When an FPGA is configured, the bits of the LUT are loaded with ones or zeros based on what the desired truth table would be. The LUT inputs act as the address lines for a corresponding one-bit-wide RAM cell. Think of the LUT as a small scratchpad RAM.

#FPGA LUT CIRCUIT PLUS#

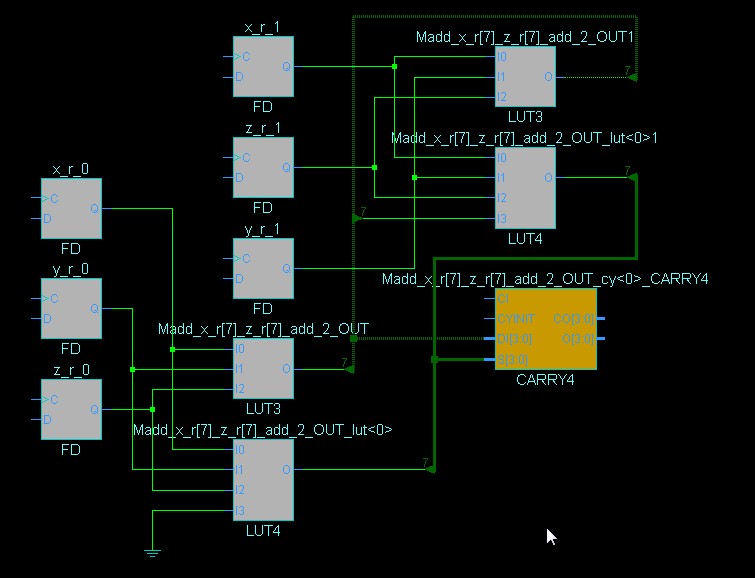

These additional functions require a true 3-input LUT, or two 2-input LUTs plus a mux. The LUT in an FPGA holds a custom truth table, which is loaded when the chip is powered up. However, this leaves 256 - 96 = 160 functions that cannot be created. Since you get to pick which of the three input variables is connected to the second LUT, you can actually create up to 32 × 3 = 96 different functions this way. A single FPGA has thousands of these components. When you cascade two 2-input LUTs, you are effectively creating a temporary variable T that is a function of two of the inputs (16 choices) and then the final output is a function of T and the third input (16 more choices), for a total of 32 choices. LUTs are one of the two most fundamental components in an FPGA. The major issue is it requires a dedicated hardware to meet the low power requirements in real-time. There are multiple issues in implementing these algorithms on digital platform. Each value represents one possible Boolean function of the three input variables.Ī 2-input LUT can contain one of 2 4 = 16 different functions. Nowadays deep learning algorithms are became popular in the field of biomedical applications for automatic classification and detection problems. Any configuration of the LUT can be rendered as digital circuit diagram. A 3-input LUT is an 8-bit memory, and that memory can contain one of 2 8 = 256 different values. FPGA devices use look-up table (LUT) to implement arbitrary combinatorial logic.

0 kommentar(er)

0 kommentar(er)